ISSN 2220-9085(ONLINE) ISSN 2412-3587(PRINT)

(IJNCAA)

# INTERNATIONAL JOURNAL OF

# NEW COMPUTER ARCHITECTURES AND THEIR APPLICATIONS

# International Journal of NEW COMPUTER ARCHITECTURES AND THEIR APPLICATIONS

#### Editor-in-Chief

Maytham Safar, Kuwait University, Kuwait Rohaya Latip, University Putra Malaysia, Malaysia

#### **Editorial Board**

Ali Sher, American University of Ras Al Khaimah, UAE Altaf Mukati, Bahria University, Pakistan Andre Leon S. Gradvohl, State University of Campinas, Brazil Azizah Abd Manaf, Universiti Teknologi Malaysia, Malaysia Carl D. Latino, Oklahoma State University, United States Duc T. Pham, University of Birmingham, United Kingdom Durga Prasad Sharma, University of Rajasthan, India E.George Dharma Prakash Raj, Bharathidasan University, India Elboukhari Mohamed, University Mohamed First, Morocco Eric Atwell, University of Leeds, United Kingdom Eyas El-Qawasmeh, King Saud University, Saudi Arabia Ezendu Ariwa, London Metropolitan University, United Kingdom Genge Bela, University of Targu Mures, Romania Guo Bin, Institute Telecom & Management SudParis, France Isamu Shioya, Hosei University, Japan Jacek Stando, Technical University of Lodz, Poland Jan Platos, VSB-Technical University of Ostrava, Czech Republic Jose Filho, University of Grenoble, France Juan Martinez, Gran Mariscal de Ayacucho University, Venezuela Kayhan Ghafoor, University of Koya, Iraq Khaled A. Mahdi, Kuwait University, Kuwait Ladislav Burita, University of Defence, Czech Republic Lenuta Alboaie, Alexandru Ioan Cuza University, Romania Lotfi Bouzguenda, Higher Institute of Computer Science and Multimedia of Sfax, Tunisia Maitham Safar, Kuwait University, Kuwait Majid Haghparast, Islamic Azad University, Shahre-Rey Branch, Iran Martin J. Dudziak, Stratford University, USA Mirel Cosulschi, University of Craiova, Romania Mohammed Allam, Naif Arab Universitgy for Security Sciences, Saudi Arabia Monica Vladoiu, PG University of Ploiesti, Romania Nan Zhang, George Washington University, USA Noraziah Ahmad, Universiti Malaysia Pahang, Malaysia Padmavathamma Mokkala, Sri Venkateswara University, India Pasquale De Meo, University of Applied Sciences of Porto, Italy Paulino Leite da Silva, ISCAP-IPP University, Portugal Piet Kommers, University of Twente, The Netherlands Radhamani Govindaraju, Damodaran College of Science, India Talib Mohammad, Bahir Dar University, Ethiopia Tutut Herawan, University Malaysia Pahang, Malaysia Velayutham Pavanasam, Adhiparasakthi Engineering College, India Viacheslav Wolfengagen, JurInfoR-MSU Institute, Russia Waralak V. Siricharoen, University of the Thai Chamber of Commerce, Thailand Wojciech Zabierowski, Technical University of Lodz, Poland Yoshiro Imai, Kagawa University, Japan Zanifa Omary, Dublin Institute of Technology, Ireland

Zuqing Zhu, University of Science and Technology of China, China

#### Overview

The SDIWC International Journal of New Computer Architectures and Their Applications (IJNCAA) is a refereed online journal designed to address the following topics: new computer architectures, digital resources, and mobile devices, including cell phones. In our opinion, cell phones in their current state are really computers, and the gap between these devices and the capabilities of the computers will soon disappear. Original unpublished manuscripts are solicited in the areas such as computer architectures, parallel and distributed systems. microprocessors and microsystems, storage management, communications management, reliability, and VLSI.

One of the most important aims of this journal is to increase the usage and impact of knowledge as well as increasing the visibility and ease of use of scientific materials, IJNCAA does NOT CHARGE authors for any publication fee for online publishing of their materials in the journal and does NOT CHARGE readers or their institutions for accessing the published materials.

#### **Publisher**

The Society of Digital Information and Wireless Communications 20/F, Tower 5, China Hong Kong City, 33 Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong

#### **Further Information**

Website: <a href="http://sdiwc.net/ijncaa">http://sdiwc.net/ijncaa</a>, Email: <a href="mailto:ijncaa@sdiwc.net">ijncaa@sdiwc.net</a>, Tel.: (202)-657-4603 - Outside USA; 001(202)-657-4603 - Outside USA.

#### Permissions

International Journal of New Computer Architectures and their Applications (IJNCAA) is an open access journal which means that all content is freely available without charge to the user or his/her institution. Users are allowed to read, download, copy, distribute, print, search, or link to the full texts of the articles in this journal without asking prior permission from the publisher or the author. This is in accordance with the BOAI definition of open access.

#### Disclaimer

Statements of fact and opinion in the articles in the International Journal of New Computer Architectures and their Applications (IJNCAA) are those of the respective authors and contributors and not of the International Journal of New Computer Architectures and their Applications (IJNCAA) or The Society of Digital Information and Wireless Communications (SDIWC). Neither The Society of Digital Information and Wireless Communications nor International Journal of New Computer Architectures and their Applications (IJNCAA) make any representation, express or implied, in respect of the accuracy of the material in this journal and cannot accept any legal responsibility or liability as to the errors or omissions that may be made. The reader should make his/her own evaluation as to the appropriateness or otherwise of any experimental technique described.

Copyright © 2017 sdiwc.net, All Rights Reserved

The issue date is September 2017.

Volume 7, Issue No. 3

2017

# CONTENTS ORIGINAL ARTICLES

| SPEEDING UP CANNY EDGE DETECTION USING SHARED MEMORY PROCESSING                                    | 58  |

|----------------------------------------------------------------------------------------------------|-----|

| DRONE ROUTE PLANNING FOR MILITARY IMAGE ACQUISITION USING PARALLEL SIMULATED ANNEALING             | 77  |

| A BIPOLAR SINGLE VALUED NEUTROSOPHIC ISOLATED GRAPHS: REVISITED                                    | 39  |

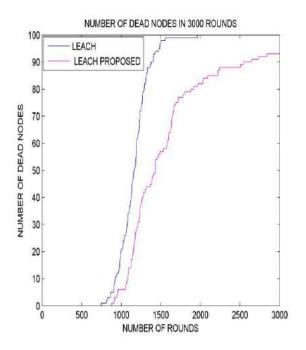

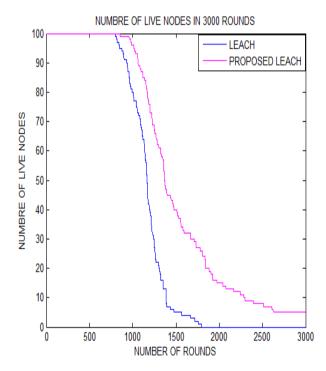

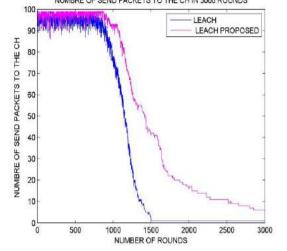

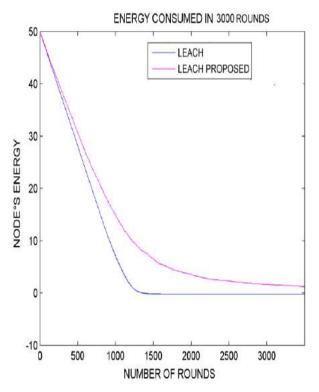

| DEVELOPMENT OF AN ALGORITHM BASED ON CONSERVATION OF ENERGY AND ON A HIERARCHICAL ROUTING PROTOCOL | 95  |

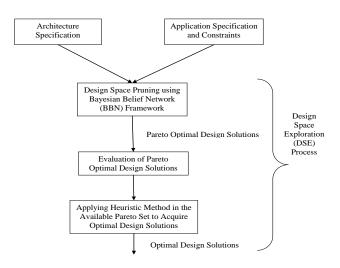

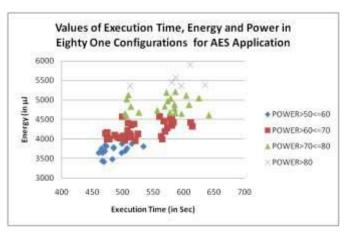

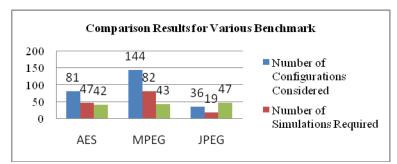

| HYBRID DESIGN SPACE EXPLORATION METHODOLOGY FOR APPLICATION SPECIFIC  SYSTEM DESIGN                | 102 |

# **Speeding Up Canny Edge Detection Using Shared Memory Processing**

Njood S. Alassmi and Soha S. Zaghloul, PhD.

College of Computer & Information Sciences, Department of Computer Science, King Saud University, Riyadh 435920199@student.ksu.edu.sa, smekki@ksu.edu.sa

#### **ABSTRACT**

Image processing is a computational operation that requires many CPU cycles for simple image transformation. It takes every pixel of an image to perform a transformation to a new image. The image can be divided into smaller chunks, with same transformation operations being implemented on each. Thus, image processing is a good candidate for running on a parallel processor to improve the speed of computation when there are multiple images to be processed. In fact, this research focuses on Canny edge detection as a case study of probing parallelism. This work presents the design and implementation of sequential and parallel edge detection algorithms that are capable of producing high-quality results and performing at high speed. Therefore, this research aims to improve the Canny edge detection algorithm in terms of speed and scalability with different sizes of images. The algorithm is implemented using Java language with the Parallel Java library. In the first phase of the project, the Canny is implemented on a sharedmemory processor. It is found that there is a valuable gained speedup with respect to the sequential version. In addition, it is found that more parallelism is explored in larger image sizes with Canny edge detector.

#### **KEYWORDS**

Canny Edge Detection, Shared-Memory, Sequential Implementation, Parallel Implementation, Parallel Java Library.

#### 1 INTRODUCTION

The growth of the world's technological industry has an important effect on our lives; we are witnessing a growth of computer power combined with a development of the digital camera abilities. Currently, it is important for a large number of users to assess the quality of acquired images. Image edge detection is one of the operations implemented with the purpose of an image refinement. The edge

detection process is significant in image analysis including texture feature extraction, image segmentation and shape feature extraction. Recently, it becomes the most effective field of the digital image processing. There are several approaches available to detect the edges of an image such as Prewitt operator, Canny operator, Roberts operator and Sobel operator. However, to create a high-quality edge detection method, more complexity is added to get high-quality that is able to be performed at high speed.

In order to achieve high performance computing (i.e. reducing computing elapsed time), parallel processing is widely used in multimedia computing, signal processing, scientific computing, engineering, general purpose application, industry, computer systems, statistical applications, and simulation [1]. The concept of parallel image processing is adapted for the purpose of fast image processing. The basic concept behind parallel computing is the distribution of the workload between the individual processors that are working together to perform computations. Various image processing techniques can be easily implemented in a parallel fashion [2]. In order to memory, shared we need apply parallel programming languages for implementation instead of the traditional sequential ones. The aim of this research is to decrease the execution time of an existing image edge detection algorithm by comparing the execution times of both the serial and parallel programs. The objectives may be listed in the following points:

- Increase the gained speedup by implementing the algorithm on a parallel environment.

- Explore the efficiency and scalability of the parallel algorithm.

• Improve the Canny edge detection algorithm in terms of speed.

This research focuses on Canny edge detection as a case study to probing parallelism. The Canny operator represents a multi-stage process. Firstly, the Gaussian filter is applied to smooth the entire image. Secondly, the gradient magnitude for the image and the upper and lower threshold values are determined. The tracking process uses hysteresis controlled by two thresholds: T1 and T2. This hysteresis helps to ensure that noisy edges are not broken up into multiple edges. Edge detection is an important area in many applications in the field of image processing. It is a foundational step for high-level information acquisition because image edges contain relevant information. Currently, it plays a critical role in many fields, such as mechanics, the military and medical diagnosis.

#### 2 REVIEW OF RELATED STUDIES

This research focuses on Canny edge detection as a case study to implement the parallelism concept. In [3], the author presented the Canny edge detection operator that used a multi-stage algorithm to detect a broad range of edges in images. The aim of Canny is to develop an optimal algorithm focusing on the following criteria: Firstly, detection (the probability of detecting real edge points) should be increased, while the probability of detecting non-edge points should be decreased. Secondly, localization defined as the detected edges should be as similar as possible to the real edges. Conversely in [4], the authors stated that Canny edge detection algorithm should have a good rate of detection with a minimum number of false edges, good localization for which proximity of the real edges and the detected edges. Finally, minimal response means one edge should be detected only once. In order to implement the Canny edge detection algorithm, a series of steps must be followed. The first is to filter out any noise in the original image before attempting to detect any edges. This can be done by applying the Gaussian filter that can be computed using a simple mask. After smoothing the image and removing the noise, the next step is to find the edge strength by measuring the gradient of the image. Subsequently, the direction of the edge should be computed using the gradient in the x and y directions. After the edge directions are known, non-maximum suppression should be applied, which is used to trace along the edge in the edge direction and suppress any pixel value. This results in a thin line in the output image. The final stage is edge tracking by hysteresis; the final edges are determined by suppressing all edges that are not associated with the definite edge [5].

In [6], the authors tried to use the Canny operator with high quality in a short time. They found that the execution time is mostly 0.2184 second for input images with a size of 512\*512 pixels. In [5], the authors discussed the advantages and disadvantages of edge detection techniques. The Sobel operator provided simplicity, as well as the detection of edges and their orientations. On the other hand, its disadvantages include being sensitive to noise and inaccurate. In contrast, the Canny operator using a Gaussian filter removes any noise in an image, yielding a better detection of edges. Y. Kong et al. [7] implemented the Canny edge detection method and found that almost 90% of the edges are correctly detected. However, disadvantages include its intensive and complex computations, ensuring that it is time consuming. The overall time complexity is found to be O (m\*n log m\*n), where m and n are the width and length of the image in terms of pixels.

Image edge detection algorithms are implemented in various parallel environments, including GPUs, SMPs, and MPPs. In [8] and [9], the authors proved the efficiency of the GPU in conducting in parallel the millions of pixel calculations involved in image processing. In [8], the authors examined the edge detection in both sequential and parallel algorithms in order to measure the speedup. The results indicate that the parallel implementation is about 262 times faster than the sequential implementation. In [9], the authors proposed a parallel Canny algorithm for the embedded CPU and GPU heterogeneous. The results

showed that the proposed parallel Canny algorithm achieved nearly 50 times speedup on the embedded systems. They used differently sized images for the tests. For 512×512 images, the runtime of a Canny algorithm in sequential implementation is found to be over 1,5898 milliseconds. Otherwise, Canny improved the runtime to a level of 3,310 milliseconds by using embedded CPUs and GPUs.

# 3 SEQUENTIAL EDGE DETECTION ALGORITHM

The applied sequential edge detector is Canny's since it is known to provide the optimal edge detector [10]. Canny's detector applies many steps before reaching the final result. The input image is read into an array of size m×n where m and n are the width and length of the image respectively in terms of number of pixels. The algorithm starts by storing the 2-D image in a 1-D array to simplify processing in later phases. Then, the algorithm visits every pixel of the image and makes the modifications as detailed below. The algorithm goes through a series of steps [11]:

- 1. Noise Removal: The first step is to filter any noise in the original image before attempting to detect edges. This is done using Gaussian filter computed by a simple mask and exclusively used in the Canny algorithm.

- **2. Gradients Calculation:** After eliminating the noise and smoothing the image, gradients of the image are taken for each edge, gradient magnitude (M) represented the edge intensity.

- **3. Thresholding:** Two thresholds are used to detect image edges. Two values, upper and lower, are specified. This allows for greater flexibility than using a single threshold approach.

- **4.Edges Classification:** The thresholding is used to detect the final edges in an image by using the two thresholding values of v\_low and v\_high. In this step, the pixels are classified into three categories in terms of the value of the magnitude M. If a pixel gradient is higher than the high threshold (M > v\_high), the pixel is accepted as a strong edge. If (v\_low \le M \le v\_high), the pixel is classified as a weak edge and waits for the judgement of the edge

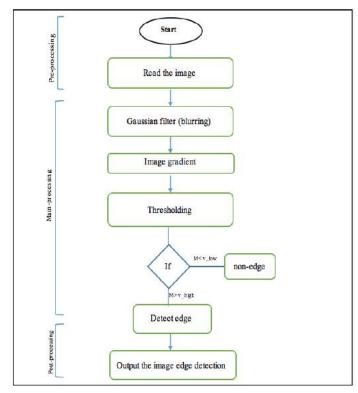

points. If (M <v\_low), the pixel is rejected if classified as a non-edge. The diagram in Fig. 1 shows the main steps of the approach for Canny edge detection.

**Figure 1.** The flow chart of the sequential version for Canny Edge Detection steps

# 4 PARALLEL EDGE DETECTION ALGORITHM USING SMP

SMP is a symmetric multiprocessor; each processor has its own cache. As the name indicates, the processors communicate with each other through a shared memory. A process is divided into threads and each thread runs on a core. Consequently, the memory can be together accessed directly by multiple processors. In this situation, communications among processors are carried out by accessing the same memory space from different processors. This scheme makes it easier for a developer to write in parallel program, by making at least the data sharing much more appropriate. An advantage of SMP is that data sharing between tasks is fast and uniform due to the closeness of memory to CPUs. On the other hand, the main disadvantage is the lack of scalability between memory and CPUs.

Parallelism is applied by looking for independency between data, especially in loop iterations. Canny edge detection algorithm is a good candidate for parallelism. The reason behind that is the available independent processing required on image pixels. On the other hand, the available hardware defines the applicable parallelism level. For example, processing an image of resolution 512×512 implies that the number of operations in a single step of Canny algorithm is 262,144. When run on dualcore computer, these computations are divided into two chunks; each of which handles 131,072 operations running simultaneously. In this phase of the research, a parallel algorithm is designed for an SMP by dividing the tasks of pixels' modifications by the number of cores. Each chunk is assigned to a core, and operations run simultaneously. In other words, each core is responsible for processing its own segment of array at the same time. Once the processing is done, the new data array is produced. The latter is then written onto a new image file, generating the image edges as detected by Canny parallel algorithm. The following pseudo-code explains the parallel Shared-memory for Canny edge detection steps using parallel java PJ2:

```

Algorithm 2: The parallel Shared-memory for Canny Edge

Detection

1- Read Input Image I;

2- Obtain the Image Size S;

3- Set the Gaussian valu, LowThreshold valu,

HighThreshold_valu;

StartTime = System.currentTimeMillis();

4- new Parallel Team ().execute (new ParallelRegion()

public void run () throws Exception

execute (0, S - 1, new IntegerForLoop ()

public void run (int first, int last)

for (int x = first; x \le last; x++)

//Apply Gaussian filter g (x, y);

public void finish ()

//Performing to get the final result after the

Parallel Job

1);

}); //end Parallel Team.

5- Apply the Parallel Team on the Gradient magnitude;

6- IF (M > v_high)

Accepted as a strong edge;

The pixel is rejected;

EndTime = System.currentTimeMillis();

7- Output the image edge detection and Time taken.

```

#### 5 EXPERIMENTAL RESULTS

#### **5.1 Software and Hardware Requirements**

In this research, the Canny image edge detector is implemented in both sequential and parallel approach. The parallel version is applied in a SMP environment. Java programming language is used in coding with the support of Parallel Java library to manage threads under Linux Ubuntu 16 operating system.

On the other hand, a Toshiba laptop featured with an Intel quad-core i5 processor with 2.4 GHz speed is used in the current phase of the research. The processor does not support hyper-threading; therefore, the maximum number of experimented threads is four. The memory capacity is 8 GBytes.

#### **5.2 Performance Measurements**

This research aims to increase the speedup, the efficiency and the scalability of the sequential code by exploring its embedded parallelism.

The performance of the parallel algorithm is measured by comparing it to the sequential algorithm. Three main metrics are used to measure such improvement; namely, the speedup, the efficiency and the scalability. These are detailed in the following sections.

#### - Speed up

In order to differentiate between the running times of the sequential and parallel algorithms, the following notations are used: T<sub>seq</sub> denotes the running time of the sequential program, and T<sub>par</sub> denotes the running time of the parallel program. The speedup (S) is defined as the ratio of the execution time of the serial implementation over the execution time of the parallel implementation. Let T (N, 1) be the time required for the best serial algorithm to solve problem of size N on one processor and T (N, K) be the time for a given parallel algorithm to solve the same problem of the same size N on K processors. Thus, speedup is defined as [12]:

$$S(N,K) = \frac{T \operatorname{seq}(N,1)}{T \operatorname{par}(N,K)} (1)$$

#### -Efficiency

Efficiency (E) is a metric that how close a program is to ideal speedup. The efficiency of a real program is less than 1. A program is close to the ideal status

as its efficiency is closer to 1. Efficiency is therefore measured using the following formula [13]:

$$E(N, K) = \frac{Actual Speedup}{Ideal Speedup} = \frac{Speedup(N, K)}{K}$$

(2)

## -Scalability

A program's size-up is the size of the parallel version running on K processors relative to the size of the sequential version running on one processor for a given running time T [13]:

Size-up (T, K) =

$$\frac{N \operatorname{par}(T,K)}{N \operatorname{seq}(T,1)}$$

(3)

#### 6 RESULTS

# **6.1 Sequential Code**

This research uses three general images of different sizes; namely, 1024x1024, 2000×2000 and 2500×2500 pixels. The initial image sizes are modified to the previously mentioned sizes using Adobe Photoshop software. Fig. 3 (a, c) show the original images; whereas Fig. 3 (b, d) expose them after applying the algorithm. It can be detected that the edges are clear in the output images. Thus, it can be concluded that the Canny algorithm is suitable for these samples of colored images.

(a) The original image with size 2000×2000 pixels.

(b) Result of Canny's algorithm.

(c) The original image with size 2500×2500 pixels.

(d) Result of Canny's algorithm

**Figure 3.** The sequential edge detection results

Experiments are applied on three image sizes to measure the running time. The results are shown in (Table 1) in the Appendix. Multiple image sizes are used to explore the relation between the image sizes and the corresponding execution times. It is found that the execution time is directly proportional with the image size. Such result is expected since the problem size increases.

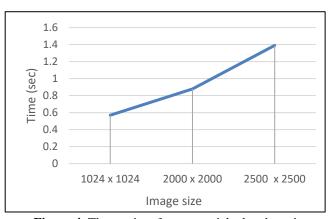

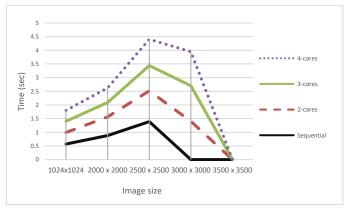

Fig. 4 shows the relation between the image size and the execution time as measured by the sequential program. The image size is in pixels whereas the execution time is measured in seconds. Expectedly, the execution time is directly proportional with the image size. Precisely, it is found that for the image size 1024×1024 pixels, it took about 0.569 seconds. While for the image size 2000×2000 pixels, the execution time took 0.868 seconds with an increase in time of 54.3% as compared to the 1024x1024 image. On the other hand, it took 1.39 seconds to detect the edges of an image of size 2500x2500 pixels. More precisely, the execution time increased by 58.3% as compared to the second image. the time Obviously, execution increases exponentially with the increase of image size.

Figure 4. The runtime for sequential edge detection

#### **6.2 Parallel Code**

In order to get accurate results, both sequential and SMP versions are tested on the same computer to exclude the hardware impact on the resulting execution times. In addition, the basic algorithm is the same in both versions. Moreover, the SMP code is tested with the same images previously used in the

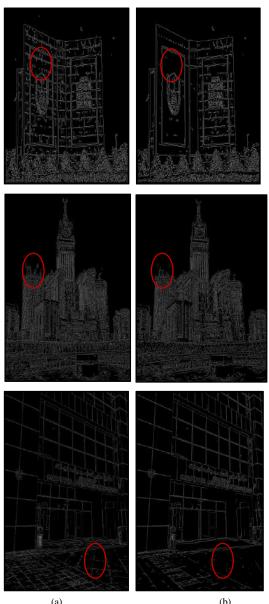

experiments of the sequential code. Fig. 5 shows the resulting detected edges using the sequential and SMP codes in (a) and (b) respectively.

Figure 5. The edge detection results by using SMP

It is noticed that there is a difference in the produced edges for each image. More precisely, the parallel implementation is less sensitive to weak edges as compared to the sequential code. Therefore, the images resulting from the parallel implementation is closer to real edges than its sequential counterpart. Table 2 in the Appendix details the experimental

results on a shared memory processor for the three

sizes of the image with various numbers of cores. The parallel code is run for each image ten times for two cores, then ten times for the three cores, and ten times on four cores. For each batch, the minimum execution time is taken. The execution times of the sequential version are added in the last row for convenience.

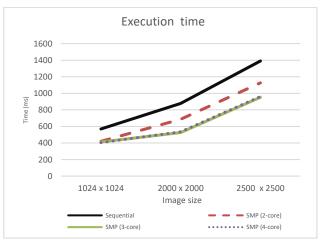

It is noticed that the execution time of the SMP code is reduced for both two and three cores as compared to the sequential version. Also, for each image size, the recorded execution time on three cores is less than its corresponding one on two cores. However, the four-core results are not always the minimum as may be expected. This may be explained by the imposed overhead of threads scheduling which increases with the increasing number of cores.

More precisely, the execution times for the image size  $1024 \times 1024$ ,  $2000 \times 2000$  and  $2500 \times 2500$  pixels are 420, 687 and 1126 respectively when run on two cores. Compared to the sequential algorithm, a reduction of 35.5%, 28.2% and 18.99%, this is decrease execution time at a rate of 35.48% for sequential execution. While the second image with the size  $2000 \times 2000$  pixels, the execution time took 678 milliseconds at a rate of decrease of 28.17% from the execution time in the sequential. The last image with size  $2500 \times 2500$  pixels, the execution time took 1126 milliseconds. The difference in execution time from the previous image is decreased by 23.45%. Also, the implementation of 3-cores has less execution time than the previous execution.

Fig. 6 depicts the results recorded in Table 2 in the Appendix. Obviously, the execution time for all image sizes is the largest in the sequential code, and the least when executed on three or four cores, since they almost have the same figures. These results are in fact expected.

**Figure 6.** Comparison between Shared-memory(SMP) and sequential execution

Table 3 in the Appendix displays the gained speedup and efficiency of the SMP Canny edge detection algorithms for the three images' sizes. The table proves experimentally that the execution time decreases with the increase of number of cores.

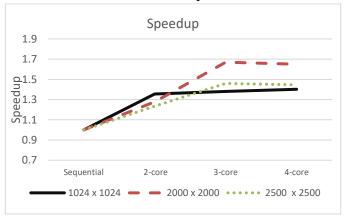

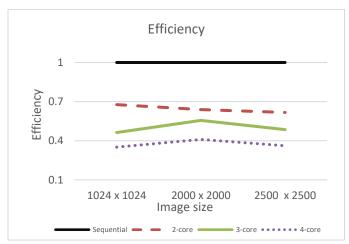

In Fig. 7, the speedup slightly increases for the  $1024 \times 1024$  image when run on four cores as compared to the 2-cores and 3-cores. The increase is higher as the image size increases. This demonstrates that more parallelism is explored in larger image sizes with Canny edge detector. Although the speedup increases with the increase of cores, but the efficiency decreases for all image sizes as shown in Fig. 8. This is also expected since the ceiling of the ideal speedup increases with larger number of cores. On the other hand, the actual speedup does not rise up equally. Therefore, the efficiency decreases with the increase of the number of processors.

**Figure 7.** The speedup of the SMP Canny edge detection algorithms

**Figure 8.** The efficiency of the SMP Canny edge detection algorithms

Fig. 7 shows that the gained speedup of using two threads is around 1.4 for the smallest image size. However, the gained speedup decreases with the increase of image size. On the other hand, the results for three-core and four-core architectures are almost the same. It is also noted that the gained speedup is around 1.6 at its maximum for an image size of 2000x2000; it then drastically degrades for the largest image size. This might be explained by the limited capabilities of the used laptop. This explanation is proved in Fig. 8, where the efficiency is at its best for two threads, and at its minimum for four threads.

Fig. 9 displays the scalability of the SMP Canny edge detection algorithms for the three images' sizes. The scalability factor, as previously explained in Section 5.2, or the sizeup efficiency, is calculated as follows:

Scalability factor (2-cores) =

$$\frac{N2}{N1} = \frac{3000}{2500} = 1.2$$

Scalability factor (3-cores) =  $\frac{N3}{N1} = \frac{3000}{2500} = 1.2$

Scalability factor (4-cores) =  $\frac{N4}{N1} = \frac{3000}{2500} = 1.2$

Where  $N_i$  represents the largest problem size that can be handled when run using i cores. As noticed, the largest problem size is 2500x2500 and 3000x3000 for sequential and multi-cores respectively. Although the largest problem size is identical for multi-cores, but the execution time decreases for this size when run on three and four cores. As previously

mentioned, the main disadvantage for SMP is the lack of scalability of memory and the number of cores/threads. Such limitations are overcome when using SANAM supercomputer as planned for the next project phase.

Figure 9. Results of parallel Scalability (Sizeup)

#### 7 CONCLUSION & FUTURE WORK

This project implements image detection twice: the first time using a sequential code, and the second time using a parallel code for a shared memory processor using 2, 3 and 4 cores. It is proved that the Canny edge detection technique performs at a higher speed in parallel environment than sequential. The performance is measured based on the speedup, efficiency and scalability. It is found the average gained speedup is equal to 1.3, 1.4, and 1.50 for two, three, and four cores respectively. Therefore, it can be concluded that the gained speedup increases with a larger number of cores. On the other hand, the experiments found that the average efficiency is 0.64, 0.50, and 0.37 for two, three, and four cores respectively. In conclusion, the efficiency decreases with the increase of the number of cores since the actual speedup does not increase at the same rate as the linear speedup.

In addition, it is found that more parallelism is explored in larger image sizes with Canny edge detector. Also, the experiments show that the sizeup efficiency is 1.2 for all number of cores used in the experiment. In fact, the main disadvantage of SMP is the lack of scalability of memory and number of cores.

In the future, a third version of Canny edge detector is to be implemented on SANAM supercomputer clusters. The objective is to explore the three previously mentioned performance metrics on a cluster environment that contains thousands of processors.

#### **REFERENCES**

- H. Khalilieh, "Performance Evaluation Of Message Passing Vs. Multithreading Parallel Programming Paradigms On Multi-Core Systems," International Journal of New Computer Architectures and their Applications, vol. 4, no. 4, pp. 108–116, 2014.

- Y.-M. Kang, "Gpu-Based Object Identification In Large-Scale Images For Real-Time Radar Signal Analysis,"

International Journal of New Computer Architectures and their Applications, vol. 6, no. 4, pp. 140–149, 2016.

- 3. Y. Cheng, "An improved Canny Edge Detection Algorithm," in Recent Advances in Computer Science and Information Engineering, vol. 126, Springer, pp. 551–558, 2012.

- Shokhan M. H.," An Efficient Approach for Improving Canny Edge Detection Algorithm," International Journal of Advances in Engineering & Technology, Vol. 7, Issue 1, pp. 59-65, 2014

- 5. M. Raman R., and H. Aggarwal. "Study and comparison of various image edge detection techniques," International journal of image processing (IJIP) Vol.3 no.1, 2009.

- M. R. Vahidi, M. M. RiahiKashani and A. Bagheri, "An efficient gradient based algorithm for improving performance of image edge detection," International Journal of Computer Applications, 103(4), 2014.

- 7. A.-A.-N., Y. Kong, and M. N. Hasan, "Performance analysis of Canny's edge detection method for modified threshold algorithms," 2015 International Conference on Electrical & Electronic Engineering (ICEEE), 2015.

- 8. A. Jain, A. Namdev and M. Chawla, "Parallel edge detection by SOBEL algorithm using CUDA C," 2016 IEEE Students' Conference on Electrical, Electronics and Computer Science (SCEECS), pp. 1-6, 2016.

- 9. D. Yuefan. "Applied Parallel Computing," Singapore, US: Imperial College Press, 2012.

- 10. A. Muntasa, "Hybrid Method Based Retinal Optic Disc Detection," International Journal of New Computer Architectures and their Applications, vol. 5, no. 3, pp. 102– 106, 2015.

- 11. G. M. H. Amer and A. M. Abushaala, "Edge detection methods," 2015 2nd World Symposium on Web Applications and Networking (WSWAN), Sousse, pp. 1-7, 2015

- 12. E. Guerrout\*, R. Mahiou and S. Ait-Aoudia, "Medical Image Segmentation on a Cluster of PCs using Markov

Random Fields," International Journal of New Computer Architectures and their Applications, pp. 35-44, 2013.

13. A. Kaminsky, "BIG CPU, BIG DATA: Solving the World's Toughest Computational Problems with Parallel Computing" 2<sup>nd</sup> ed, Boston, MA: Course Technology, Cengage Learning, 2015.

#### **APPENDIX**

**Table 1.** The execution time of the sequential edge detection.

| Image size | 1024 × 1024 | 2000×2000 | $2500 \times 2500$ |

|------------|-------------|-----------|--------------------|

| / #        |             |           |                    |

| 1          | 581         | 924       | 1454               |

| 2          | 629         | 878       | 1461               |

| 3          | 599         | 883       | 1433               |

| 4          | 577         | 884       | 1422               |

| 5          | 593         | 910       | 1390               |

| 6          | 583         | 937       | 1412               |

| 7          | 585         | 880       | 1478               |

| 8          | 598         | 891       | 1440               |

| 9          | 567         | 882       | 1400               |

| 10         | 589         | 905       | 1412               |

| Minimum    | 569ms       | 878ms     | 1390ms             |

**Table 2.** The execution time for Shared memory(SMP).

| Image size | 1024×1024 |         | 4       | 2       | 2000×2000 |         | 2       | 500×2500 |         |

|------------|-----------|---------|---------|---------|-----------|---------|---------|----------|---------|

| /#         | 2-cores   | 3-cores | 4-cores | 2-cores | 3-cores   | 4-cores | 2-cores | 3-cores  | 4-cores |

| 1          | 446       | 416     | 439     | 716     | 566       | 571     | 1165    | 1062     | 981     |

| 2          | 425       | 432     | 438     | 719     | 551       | 544     | 1194    | 1099     | 992     |

| 3          | 441       | 433     | 433     | 688     | 557       | 542     | 1170    | 1052     | 983     |

| 4          | 451       | 419     | 413     | 665     | 526       | 567     | 1176    | 1017     | 974     |

| 5          | 444       | 418     | 419     | 687     | 558       | 553     | 1126    | 966      | 961     |

| 6          | 424       | 412     | 429     | 684     | 547       | 543     | 1154    | 1002     | 972     |

| 7          | 424       | 423     | 410     | 735     | 568       | 551     | 1188    | 977      | 983     |

| 8          | 420       | 424     | 422     | 671     | 568       | 543     | 1150    | 1025     | 974     |

| 9          | 437       | 432     | 406     | 681     | 586       | 535     | 1153    | 952      | 991     |

| 10         | 457       | 426     | 420     | 696     | 584       | 550     | 1144    | 977      | 979     |

| Minimum    | 420ms     | 412ms   | 406ms   | 687ms   | 526ms     | 535ms   | 1126ms  | 952ms    | 961ms   |

| Sequential | 569ms     |         |         | 878ms   |           |         | 1390ms  |          |         |

**Table 3.** Results of parallel execution time, speedup and efficiency.

| Image size | Number of cores | Execution time(milliseconds) | Speedup | Efficiency |

|------------|-----------------|------------------------------|---------|------------|

| 1024x1024  | 1 (Sequential)  | 569                          | 1       | 1          |

| pixels     | 2               | 420                          | 1.355   | 0.677      |

|            | 3               | 412                          | 1.381   | 0.463      |

|            | 4               | 406                          | 1.402   | 0.351      |

| 2000x2000  | 1 (Sequential)  | 878                          | 1       | 1          |

| pixels     | 2               | 687                          | 1.278   | 0.639      |

| Ì          | 3               | 526                          | 1.670   | 0.556      |

|            | 4               | 535                          | 1.641   | 0.410      |

| 2500x2500  | 1 (Sequential)  | 1390                         | 1       | 1          |

| pixels     | 2               | 1126                         | 1.235   | 0.617      |

| Í          | 3               | 952                          | 1.460   | 0.486      |

|            | 4               | 961                          | 1.446   | 0.362      |

# Drone Route Planning for Military Image Acquisition Using Parallel Simulated Annealing

Eman Alsafi and Soha S. Zaghloul, PhD King Saud University 435204448@student..ksu.edu.sa smekki@ksu.edu.sa

#### **ABSTRACT**

Recently, drones became one of the most interesting technologies used in diverse applications. One of the major challenges associated with them is to set a short route plan in the minimum period of time. This is an important inquiry in many applications, especially in military ones. On the other hand, the simulated annealing algorithm is one of the metaheuristics selected to generate a feasible solution to solve such problem. However, the algorithm requires long execution time. Therefore, the simulated annealing algorithm is parallelized in order to find a suitable solution of the problem in less time. Parallel programming divides the problem into smaller independent tasks, and then executes the subtasks simultaneously. Three performance metrics are used to measure the effectiveness of the parallel program; namely, the gained speedup, the efficiency and the scalability. Experiments are conducted to compare the performance of the sequential and parallel version of simulated annealing algorithm. In this paper, the algorithm is implemented on a sharedmemory processor environment. The results reported in this research show that the performance of the parallel simulated annealing on shared memory processor is higher than its sequential counterpart in almost all aspects. In addition, the given final distance is less than the sequential simulated annealing.

#### **KEYWORDS**

Parallel programming, shared memory, simulated annealing, parallel java.

### 1 INTRODUCTION

Within the past decade, drones became one of the most interesting technologies. Drones are remotely controlled pilotless aircrafts. They are usually associated with sensors and devices such as cameras, computing units, communication tools, and others [1, 2]. Drones are utilized in diverse military and civil applications. Examples include, but are not limited to, aerial surveillance,

image acquisition, remote sensing, and other aspects of scientific research [2]. Drones gained such popularity because they have several advantages over traditional aircrafts; the most important of which is saving human lives in dangerous areas and completing missions quickly with minimum cost [1, 3]. On the other hand, drones have a few limitations; such as limited flight time and energy. Therefore, one of the main challenges when dealing with drones is to find an effective route plan in a suitable amount of time [4].

As drones usually follow preloaded instructions without human intervention, the route plan may be generated either online during the flight, or offline before taking off. Moreover, drones route planning becomes more challenging when there are several geographical locations to be visited that are dispersed apart; these are called waypoints [2]. The aim of this research is to find a route plan that allows drones to acquire images from predefined waypoints in the least possible amount of time. In addition, each waypoint is to be visited exactly once. Obviously, this is the well-known Travelling analogous to Salesman Problem (TSP). Finding a nearoptimum route plan is necessary to minimize the drone's power consumption during the flight in order to cover the largest possible geographical area; and therefore, visit the largest number of targeted waypoints.

However, solving TSP problem using a bruteforce approach requires a significant amount of time to try every possible solution [2]. This approach is not suitable for the problem in-hands, since time and secrecy are both important factors in military applications. Therefore, a metaheuristics algorithm, the simulated annealing (SA) algorithm is used. In fact, SA is capable of finding an acceptable local optimum route plan [5]. Although SA is used to solve several complex problems, but it requires significant processing time to find a suitable solution [6]. In order to overcome such drawback, parallel computing is expected to positively contribute in the solution of this problem. Parallelism may minimize the execution time to fulfill the requirements of the military mission. In addition, it may increase the chance to provide a better-quality plan. However, one of the big challenges associated with parallel SA is that the SA is inherently sequential as each new solution depends on the previous one. The improvement of the parallel computational power has the ability to overcome this challenge.

In parallel computing, the problem under consideration is divided into several independent tasks that are executed simultaneously. Therefore, the execution time is expected to reduce. Obviously, more resources are needed as compared to the sequential environment. So, scalability and efficiency also increase. Three performance metrics are used to measure the effectiveness of a parallel algorithm; namely, the speedup, the efficiency, and the scalability. Speedup measures the extent of the execution time reduction of the parallel algorithm as compared to its sequential counterpart. The efficiency measures the resources utilization extent of the parallel program to the available hardware. Finally, the scalability measures the ability of the parallel program to handle larger problem sizes. So, the target of this research is to maximize the three previously mentioned metrics [7].

Since the main target is to generate a route plan for military drones emitted with the intention of acquiring images at multiple sites; time and energy are therefore critical factors. Thus, they are also taken into consideration in addition to finding a good solution.

This paper is structured as follows: Section 2 exposes the related work in the literature. Section 3 details the solution's design for both sequential and SMP algorithms. Section 4 introduces the results of both sequential and SMP versions. Finally, the conclusion and future work are summarized in Section 5.

#### 2 Related Work

The drone route planning problem in this research is analogous to the TSP. There are several

algorithms that provide a solution for the TSP, such as LS, BB, EAs, ACO, and hybrid algorithms [7]. This chapter exposes the sequential and parallel solutions to the TSP in general, and to the drone route planning in particular.

Many sequential algorithms are proposed to solve the TSP, some of which are based on the ACO algorithm. The proposed solution in [8] provides a modification of the traditional ACO method; this is known as the High Performance ACO. The traditional ACO algorithm involves a single ant randomly looking for the path; whereas the updated algorithm applies the TSP on a group of ants. The authors provide a comparison between their proposed algorithm and the ant colony system algorithm on various numbers of nodes. They found that the proposed algorithm completes the task in less time.

Also, Local search algorithms are widely used to solve the TSP. The research in [7] provides an experimental study to test the performance of the Lin-Kernighan and the Multi-Neighborhood Search. Results show that the Lin-Kernighan provides better results than the Multi-Neighborhood Search in terms of runtime.

On the other hand, several parallel solutions are proposed in the literature to solve the TSP using diverse parallel programming platforms. In [46], the experiment is performed on a standard multicore CPU. The reported results indicate that a speedup of 7.3 is gained on 8 cores. Thus, the usage of PSO algorithm is more suitable for realtime planning for the drone. Moreover, the experiments also proved that the performance of the GA is better than the PSO. The same authors improved their results in [9] by proposing a parallel hybrid algorithm that exploits the advantages of both the PSO and the GA to generate a suitable path plan for fixed-wing drones. It is found that the gained speedup is 10.7 on a 12-core SMP.

In [2], the authors planned the drone's path using parallel ACO solution using a Graphical Processing Unit (GPU) platform. The generated path guides the drone in disseminating keys and collecting data from wireless sensors, which were previously deployed at minimum cost. The drone launches from a ground station, visits all sensors in a limited period of time, and then returns back to the ground station. In their experiment, the

researchers compared the sequential with the parallel performance. They showed that the speedup is higher when using GPU platform.

In [5], the authors generate multiple route paths for several drones simultaneously using synchronous parallel SA on the GPU. Experiments' results prove that the processing time is reduced and a better solution is acquired, as compared to the CPU implementation.

# 3 Design and Implementation

This section discusses the general design of SA. Then, the implementations in both sequential and SMP environments are discussed. In addition, the drone's energy manipulation is discussed.

# 3.1 Simulated Annealing Design

Two concepts are to be defined when it comes to designing an iterative metaheuristics algorithm; namely, the solution representation and the objective function. Since SA is classified as a single-solution based metaheuristics, it requires the definition of the neighborhood. These are detailed in the following subsections [10].

# 3.1.1 Solution Representation

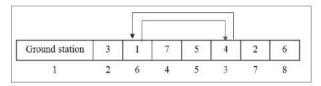

The solution representation of the drone route planning is a permutation of size n, where n is the number of the waypoints to be visited exactly once. Each permutation represents one solution as shown in Figure 1 as a sequence of nodes; where each node represents a waypoint and its index represents the corresponding order. The number of all permutations that represent the solution space taking into consideration the fixed start point (ground station) is (n-1)!

**Figure 1.**The permutation representation of the drone route plan problem

# 3.1.2 Neighborhood Solution

The neighborhood of a solution is found by performing a move operator which leads to a tiny perturbation to the solution S [10]. As the drone route plan is represented by a permutation, a neighborhood is generated by the swap operator between two elements in the solution as illustrated in Figure 2.

**Figure 2.**Neighbourhood solution generated by swapping the order of two waypoints

#### 3.1.3 Objective function

The objective function is used to define the goal to be achieved by the SA. The goal of the problem in-hands is looking for the shortest route plan for a drone such that it visits each waypoint exactly once. As previously mentioned, this is similar to the TSP and has a similar objective function which is shown below:

$$f(\pi) = Min \sum_{i=1}^{n-1} d_{\pi(i)\pi(i+1)} + d_{\pi(n)\pi(1)}(1)$$

where:

$\pi$  is a permutation that represents a tour of the drone;

and n is the number of waypoints.

#### A. Sequential simulated annealing

In order to be able to measure the speedup of the parallel SA, the sequential implementation is to be developed. As mentioned previously, the SA, like other single-solution-based metaheuristics, includes two main steps. The first step is to generate the initial solution. The latter is constructed by either using a greedy heuristic, such as the nearest neighbor algorithm or randomly. In this research, the random method is used because the greedy heuristics produce a solution in the local optimum; this may not be able to provide an improved local optimum solution at the end [10].

The second step, which is the solution improvement, the design uses the swap operator between two points to generate a neighbor solution from the current solution.

The SA algorithm imitates the process of the solid hardening, which depends on the initial temperature value and the cooling rate. Therefore, the SA implementation consists of two main loops to provide a suitable solution. The outer loop, known as the cooling loop, is responsible for managing the temperature value. On the other hand, the inner loop, known as the equilibrium state loop, is responsible for constructing a

neighbor solution from the current one, evaluating it, and computing the probability of the acceptance using the following formula:

$$e^{(-\Delta/T)} \qquad (2)$$

where:

$\Delta$  is the difference between the cost of the old and the new solution:

T is the current temperature

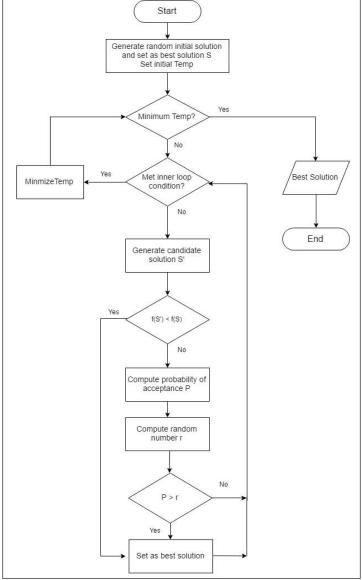

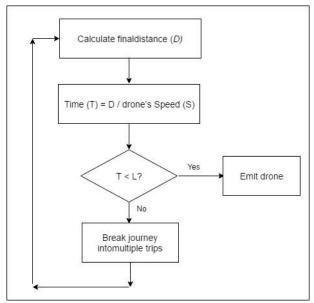

Accordingly, the main parameters that are to be defined during SA implementation are the initial temperature, the cooling rate, and the stopping condition. The latter might be the minimum temperature or a specific number of iterations. In this research, the stopping condition is taken based on a minimum temperature. Usually, The other parameters are determined after several experiments [6]. The flowchart of the sequential algorithm is shown in Figure 3.

#### B. Parallel Simulated Annealing

Metaheuristic algorithms are sequential by nature; SA is no exception. Consequently, parallelizing the SA entails a challenging problem [11]. Many approaches are proposed to parallelize SA algorithm [12]. These are summarized below:

- Decompose the search space into smaller parts, and then assign each part to a processor to find the minimum cost. The results are then shared with other processors.

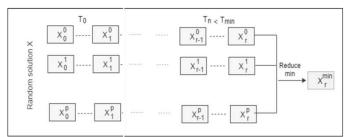

- Apply the asynchronous approach, where each processor executes SA independently. The initial solution may be either the same or different across the processors. Finally, compute a reduce operation to get the best solution among them. As illustrated in Figure 4.

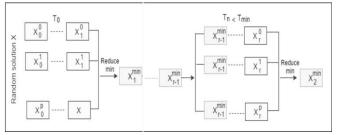

- Apply the synchronous approach, where each processor uses the same initial solution and performs parallel improvements within the same

Figure 3. Flow chart of the SA algorithm

temperature. Then at each temperature value, the best solution is shared between the processors to perform parallel improvement until the end. Figure 5 illustrates the synchronous approach.

Figure 4. Asynchronous SA parallel approach

Figure 5. Synchronous SA parallel approach

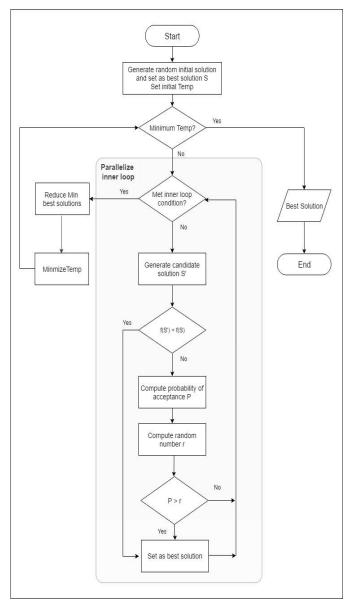

In this study, synchronous SA parallel approach is used as it is able to parallelize the equilibrium state loop. The flowchart of the parallel SA algorithm is shown in Figure 6.

Figure 6. Flowchart of parallel SA approach

#### 3.3 Handling the Drone Energy Constraints

After generating the route plan using SA algorithm at the ground station, the route is evaluated in terms of the energy required to

complete the planned mission. If the energy level is above a predefined threshold, then the drone is emitted according to the planned route. Otherwise, the mission is divided into multiple journeys. The drone is re-charged after the end of each trip, before starting a new one.

In fact, the drone's energy is expressed in terms of its enduring lifetime L. Therefore, the time *T* needed to travel the final distance *D*, as planned by the SA, is calculated as follows:

$$T = D/S \qquad (3)$$

where:

- *T* is the time required to make the complete tour calculation, including the return trip to the ground station.

- *D* is the final distance as calculated by the SA algorithm

- S is the drone's speed as specified in its specifications

If the calculated time T is less than the drone's enduring lifetime L, then the drone is safely launched. Otherwise, the journey is broken into multiple trips. Figure 7 illustrates the previously mentioned steps.

Figure 7. Checking drone's energy

Therefore, the applied predefined threshold is the enduring lifetime of the emitted drone.

#### 4 Experiments and Result

This section details the methodology used in the conducted experiments. In addition, the obtained results are discussed, analyzed and represented graphically. The first subsection reveals the

deployed environment in terms of software and hardware specifications. Subsection 4.2 exposes the performance metrics used to measure the effectiveness of the developed algorithm. Finally, subsection 4.3 details the results of both the sequential and parallel algorithm. These are presented graphically, analyzed, and then discussed in detail.

# 4.1 Software and Hardware Specification

This research is implemented on an Intel quadcore i7, with a speed of 2.53 GHz, and supports hyperthreading. The program is coded in Java under Linux ubuntu 16. PJ2 is the used multithreading library. PJ2 manages the threads by taking care of synchronization and load balancing [11]. As a result, this minimizes the idle time of the processors, increases the utilization of the hardware resources. Obviously, this is one of the significant objectives in parallel computing [13].

#### 4.2 Performance Measurements

The main objective of this research is to minimize the execution time, increase resources utilization, and increase scalability. These are measured by the speedup, the efficiency, and the sizeup respectively. The following subsections expose more details about performance measurements [11].

#### 4.2.1 Speedup

Speed up is used to measure the extent of the time reduction gained from the parallel implementation as compared to its sequential counterpart. The gained speed up is calculated using the following formula [11, 14]:

Speedup =

$$\frac{\text{Execution time of sequential version}}{\text{Execution time of parallel version}}$$

(4)

#### 4.2.2 Efficiency

The efficiency (E) is used to measure how a program is close to the ideal status. In other words, it indicates the effectiveness of the resources utilization by the parallel program. The ideal program efficiency is equal to 1. However, the actual efficiency is between 0 and 1. Efficiency is directly proportional with the use of the available hardware resources, such as the number of cores/processors. Efficiency is computed using the following formula [11]:

Efficiency =

$$\frac{\text{Actual Speed up}}{\text{Number of cores or processors}}(5)$$

#### 4.2.3 Scalability

Scalability is the ability of a program to adapt to the increasing amount of problem size. Also, it is used to measure the ability of a program to making use of the increasing number of cores/processors. The scalability is calculated according to the following formula [11]:

Scalability =

$$\frac{\text{Npar}}{\text{Nseq}}(6)$$

where:

- *Nseq* is the largest problem size that can be handled by the sequential program

- *Npar* is the largest problem size that can be handled by the parallel program for a specific number of threads.

It is expected that the problem size increases with the increase of the number of threads/processors.

#### 4.3 Methodology

The execution time of a parallel program is hardly the same when run multiple times successively. This is because the operating system is conducting its own activities at the same time as the program runs. Since these activities differ from a run to another, the resulting execution time is directly affected. The interference of the operating system always increases the resulting execution time. Therefore, the following methodology is followed to measure the execution time of a program as accurate as possible: the program is run multiple times – from 7 to 10 times – and the execution time is recorded after each run. Then, the minimum of these recordings is taken since this represents the less interference from the part of the operating system. The speedup and the efficiency are then calculated according to formulae 4 and 5 respectively.

On the other hand, the following steps are performed to measure the scalability, or the sizeup. The sequential version of the program is run multiple times while increasing the problem size in each run. The largest problem size that can be handled by the sequential program, say *Nseq*, is then recorded. The same procedure is repeated for different number of threads to get *Ni,par* where *i* represents the used number of threads.

The sizeup efficiency is then calculated according to formula 6.

#### 4.4 Experimental results

A set of experiments are conducted according to the methodology detailed in Section 4.3 with the aim of measuring the three main performance metrics: speedup, efficiency, and scalability in addition to the quality of the solution. The results of both versions of the SA algorithm are reported in the following subsections. The number of threads in the experiments range from 2 to 8.

#### 4.4.1 Running Time Measurement

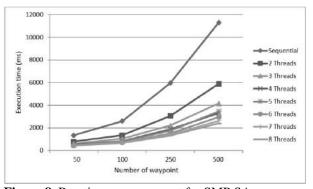

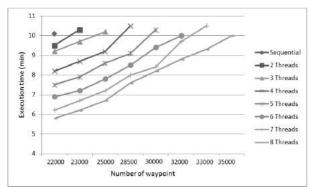

The first set of experiments aims to explore the impact of the number of waypoints on the execution time. Therefore, the program is run multiple times with various number of waypoints; namely, 50, 100, 250, and 500. For each problem size, the experiment is repeated as explained in Section 4.3. Table 1 in the Appendix shows the minimum execution time for each number of threads with the total route plan distance. Note that all the parameters of SA are fixed and chosen after several experiments to ensure the quality of the final solution. Figure 8 shows the impact of the number of waypoints on the execution time.

As seen in the graph depicted in Figure 8, the execution time of both sequential and SMP SA is proportional to the problem size. However, it is noticed that the increasing rate of the execution time of the sequential SA is higher as compared to that of the SMP SA for all threads. Table 2 in the Appendix details the increasing rates for each number of threads and for different problem sizes. Also, it is noticed from the graph that the execution time decreases with the increase of the number of threads. However, this rate decreases with the increasing number of threads.

Figure 8. Run time measurement for SMP SA

#### 4.4.2 Quality of the Route Plan

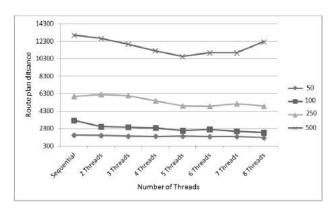

The final distance values are also depicted in Table 1 in the Appendix with various numbers of threads and waypoints. The corresponding graph is shown in Figure 9. It is noticed that the quality of the route plan is improved with the parallel execution for 81.25% of the reported results against degradation for 8.75% of the cases. Although the numbers of threads displayed on the x-axis are discrete in nature, however, the lines are represented continuous to illustrate the discrepancy between the recorded results. Also, it is noticed that the final distance increases with the increase of waypoints for all number of threads. This is expected since as, previously mentioned; the running time is directly proportional with the problem size.

Figure 9. Quality of the final distance on SMP SA

#### 4.4.3 Speedup Measurement

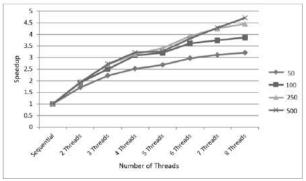

The gained speedup is calculated from the values recorded in Table 1 in the Appendix according to formula 4. Table 3 in the Appendix reports the calculations of the speedup for various numbers of cities and threads. Figure 10 depicts the same values graphically. It is noticed that the speedup is directly proportional to the number of deployed threads for all problem sizes. However, the increase rate of the speedup is less for higher values of thread numbers. These results are expected since the threads scheduling becomes more complicated for higher number of threads. Therefore, the imposed overhead is higher.

Figure 10. Speedup of SMP SA

#### 4.4.4 Efficiency Measurement

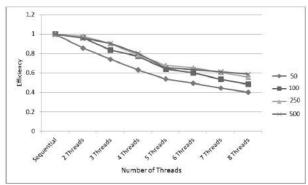

As previously mentioned, the efficiency is measured according to formula 5. The results of the calculations for all numbers of threads and waypoints are depicted in Table 3 in the Appendix. The corresponding graph is depicted in Figure 11. It is noticed that the efficiency decreases with the increase of number of threads. This is expected since the actual speedup grows at a lower rate than that of the ideal speedup. This is due to the growing complexity of threads scheduling with higher number of threads. Therefore, the gap becomes larger.

Also, it is noticed that the efficiency is close to 1 for number of threads = 4. This is explained by the fact that the SMP on which the experiments are executed is a quad-core. Since the processor supports hyperthreading, it allows us to increase the number of threads to 8 on 4 cores. However, hyperthreading is expensive in terms of scheduling, and does not yield the same efficiency if compared with an 8-core processor. Also, it is noted from the graph that the efficiency tends to zero as the number of threads increases.

Worth to mention that although the efficiency is equal to 1 for the sequential program, but this does not imply that the program makes full use of the available hardware resources. However, the actual speedup of the sequential program and the number of cores are both equal to one.

Figure 11. Efficiency of the SMP SA

### 4.4.5 Scalability Measurement

Since the hardware resources increase in an SMP, it is expected to handle larger problem sizes. The largest number of waypoints handled by each thread is divided by that handled by the sequential program. The results and calculations are reported in Table 4 in the Appendix. In addition, Figure 12 depicts the relationship between the maximum numbers of waypoints for each thread against the execution time. According to the results, the scalability is directly proportional to the number of threads. Also, it is noted that for the same number of waypoints, the execution time is reduced as the number of threads increases.

Figure 12. Scalability of the SMP SA

#### 5 Conclusion and Future Work

This research targets for generating a minimum route plan distance for a single drone emitted by a military organism for image acquisition. The area in concern may be a sensitive site, a defense and/or attack war front, or an enemy's territory. Therefore, the route path should be completed in the least possible amount of time. The SA algorithm is implemented to solve this problem which is analogous to the TSP. Since metaheuristics require an extensively long time for execution, parallel computing is deployed to

accelerate the SA algorithm. However, one of the big challenges associated with parallel SA is the inherent sequential nature of the SA. This is each new solution depends on the previous one. This research implements parallel SA using parallel java library pj2 under Linux Ubuntu on an SMP. A quad-core laptop is used whose processor supports hyperthreading.

Three main performance metrics are used to measure the effectiveness of a parallel program; namely, the gained speedup, the efficiency, and the scalability. All metrics are to be maximized. The reported results prove that the gained speedup and the scalability increase with the increase of number of threads for all numbers of waypoints. On the other hand, the efficiency decreases with the increase of number of threads due to that the actual speedup does not grow at the same rate as the linear speedup. Furthermore, the quality of the SMP SA generated final solution is increased in 81.25% of the experiments.

In the future, the SA is to be implemented on KACST's SANAM supercomputer which embraces more than three-thousands processors. The gained speedup, the efficiency, the scalability and the quality of the route plan are investigated on the supercomputer. Results are to be compared with those of SMP and those reported in the literature.

#### REFERENCES

- [1] N. Özalp and O. K. Sahingoz, "Optimal UAV path planning in a 3D threat environment by using parallel evolutionary algorithms," in *Unmanned Aircraft Systems (ICUAS)*, 2013 International Conference, 2013, pp. 308-317.

- [2] M. O. UgurCekmez, "A UAV Path planning with parallel ACO algorithm on CUDA platform," presented at the IEEE Unmanned Aircraft Systems (ICUAS), FL, USA, 2014.

- [3] M. Coeckelbergh, "Drones, information technology, and distance: mapping the moral epistemology of remote fighting," *Ethics and information technology*, vol. 15, pp. 87-98, Jun 2013.

- [4] X.-f. Liu, Z.-w. Guan, Y.-q. Song, and D.-s. Chen, "An optimization model of UAV route planning for road segment

- surveillance," *Journal of Central South University*, vol. 21, pp. 2501-2510, Jun 2014.

- [5] T. Turker, G. Yilmaz, and O. K. Sahingoz, "GPU-Accelerated Flight Route Planning for Multi-UAV Systems Using Simulated Annealing," in *International Conference on Artificial Intelligence: Methodology, Systems, and Applications*, 2016, pp. 279-288.

- [6] M. Sanjabi, A. Jahanian, S. Amanollahi, and N. Miralaei, "ParSA: parallel simulated annealing placement algorithm for multi-core systems," in *Computer Architecture and Digital Systems (CADS)*, 2012 16th CSI International Symposium, 2012, pp. 19-24.

- [7] Y. Wu, T. Weise, and R. Chiong, "Local search for the Traveling Salesman Problem: A comparative study," in 2015 IEEE 14th International Conference on Cognitive Informatics & Cognitive Computing (ICCI\*CC), Beijing, China, 2015, pp. 213-220.

- S. K. Sahana and A. Jain, [8] "High performance ant colony optimizer (HPACO) for travelling salesman (TSP)," problem in **International** Conference in Swarm Intelligence, 2014, pp. 165-172.

- [9] V. Roberge, M. Tarbouchi, and F. ALLAIRE, "Parallel hybrid metaheuristic on shared memory system for real-time UAV path planning," *International Journal of Computational Intelligence and Applications*, vol. 13, p. 1450008, Jun. 2014.

- [10] E.-G. Talbi, *Metaheuristics: from design to implementation* vol. 74: John Wiley & Sons, 2009.

- [11] A. Kaminsky, "BIG CPU, BIG DATA: Solving the World's Toughest Computational Problems with Parallel Computing," 2016.

- [12] A. Ferreiro, J. García, J. G. López-Salas, and C. Vázquez, "An efficient implementation of parallel simulated annealing algorithm in GPUs," *Journal of Global Optimization*, vol. 57, pp. 863-890, Nov. 2013.

- [13] L. O. Mafteiu-Scai, "A parallel load balancing based on pseudo-cliques," *IJNCAA*, p. 94, 2015.

- [14] S. Rastogi and H. Zaheer, "Significance of parallel computation over serial computation," in *Electrical, Electronics, and Optimization Techniques (ICEEOT), International Conference*, 2016, pp. 2307-2310.

- [15] E.-H. Guerrout, R. Mahiou, and S. Ait-Aoudia, "Medical image segmentation on a cluster of PCs using Markov random fields," *International Journal of New Computer Architectures and their Applications (IJNCAA)*, vol. 3, pp. 35-44, 2013.

# **APPENDIX**

Table 1 Minimum execution time of the serial and parallel SA with the route distance

| #waypoints #Threads | 50      |          | 100     |          | 250     |          | 500      |          |

|---------------------|---------|----------|---------|----------|---------|----------|----------|----------|

|                     | Time    | Distance | Time    | Distance | Time    | Distance | Time     | Distance |

| Sequential (1)      | 1351 ms | 1565     | 2609 ms | 3243     | 5976 ms | 5997     | 11305 ms | 13006    |

| 2                   | 788 ms  | 1536     | 1355 ms | 2531     | 3059 ms | 6209     | 5900 ms  | 12634    |

| 3                   | 607 ms  | 1442     | 1041 ms | 2467     | 2210 ms | 6072     | 4164 ms  | 11965    |

| 4                   | 535 ms  | 1426     | 844 ms  | 2389     | 1896 ms | 5478     | 3512 ms  | 11213    |

| 5                   | 502 ms  | 1430     | 814 ms  | 2076     | 1758 ms | 4913     | 3465 ms  | 10573    |

| 6                   | 454 ms  | 1399     | 723 ms  | 2215     | 1523 ms | 4867     | 2960 ms  | 10986    |

| 7                   | 434 ms  | 1386     | 696 ms  | 2011     | 1404 ms | 5148     | 2636 ms  | 10969    |

| 8                   | 420 ms  | 1269     | 675 ms  | 1856     | 1342 ms | 4875     | 2398 ms  | 12254    |

Table 2 Increase rate in the execution time for multiple threads and problem sizes

| #waypoints #Threads | 50-100 | 100-250 | 250-500 |

|---------------------|--------|---------|---------|

| Sequential (1)      | 93.1%  | 129 %   | 89.1 %  |

| 2                   | 71.9 % | 125.7 % | 92.8 %  |

| 3                   | 71.4 % | 112.2 % | 88.4 %  |

| 4                   | 57.7 % | 124.6 % | 74.7 %  |

| 5                   | 62.1%  | 115.9 % | 85.2%   |

| 6                   | 59.2 % | 110.6 % | 94.3%   |

| 7                   | 60.3 % | 101.7 % | 87.7 %  |

| 8                   | 60.7 % | 98.8 %  | 78.6 %  |

Table 3 Measure performance of parallel SA on SMP (speedup-efficiency)

| #waypoints  | # Threads      | Execution time (ms) | Speedup  | Efficiency |

|-------------|----------------|---------------------|----------|------------|

|             | Sequential (1) | 1351 ms             | 1        | 1          |

|             | 2              | 788 ms              | 1.714467 | 0.857234   |

|             | 3              | 607 ms              | 2.2257   | 0.7419     |

|             | 4              | 535 ms              | 2.525234 | 0.631308   |

| 50          | 5              | 502 ms              | 2.691235 | 0.538247   |

|             | 6              | 454 ms              | 2.975771 | 0.495962   |

|             | 7              | 434 ms              | 3.112903 | 0.4447     |

|             | 8              | 420 ms              | 3.216667 | 0.402083   |

|             | Sequential (1) | 2609 ms             | 1        | 1          |

|             | 2              | 1355 ms             | 1.925461 | 0.962731   |

|             | 3              | 1041 ms             | 2.506244 | 0.835415   |

| 100         | 4              | 844 ms              | 3.091232 | 0.772808   |

| 100         | 5              | 814 ms              | 3.20516  | 0.641032   |

|             | 6              | 723 ms              | 3.608575 | 0.601429   |

|             | 7              | 696 ms              | 3.748563 | 0.535509   |

|             | 8              | 675 ms              | 3.865185 | 0.483148   |

|             | Sequential (1) | 5976 ms             | 1        | 1          |

|             | 2              | 3059 ms             | 1.95358  | 0.97679    |

|             | 3              | 2210 ms             | 2.704072 | 0.901357   |

| 250         | 4              | 1896 ms             | 3.151899 | 0.787975   |

|             | 5              | 1758 ms             | 3.399317 | 0.679863   |

|             | 6              | 1523 ms             | 3.923835 | 0.653972   |

|             | 7              | 1404 ms             | 4.25641  | 0.608059   |

|             | 8              | 1342 ms             | 4.453055 | 0.556632   |

|             | Sequential (1) | 11305 ms            | 1        | 1          |

|             | 2              | 5900 ms             | 1.916102 | 0.958051   |

|             | 3              | 4164 ms             | 2.714938 | 0.904979   |

| <b>5</b> 00 | 4              | 3314 ms             | 3.218964 | 0.804741   |

| 500         | 5              | 3465 ms             | 3.262626 | 0.652525   |

|             | 6              | 2960 ms             | 3.819257 | 0.636543   |

|             | 7              | 2636 ms             | 4.288695 | 0.612671   |

|             | 8              | 2398 ms             | 4.714345 | 0.589293   |

Table 4 Measure scalability of parallel SA on SMP

| # Threads      | Size up | Scalability |

|----------------|---------|-------------|

| Sequential (1) | 22000   |             |

| 2              | 23000   | 1.05        |

| 3              | 25000   | 1.14        |

| 4              | 28000   | 1.28        |

| 5              | 30000   | 1.34        |

| 6              | 32000   | 1.46        |

| 7              | 33000   | 1.5         |

| 8              | 35000   | 1.6         |

# A Bipolar Single Valued Neutrosophic Isolated Graphs: Revisited

Said Broumi

Laboratory of Information Processing, Faculty of Science Ben M'Sik, University Hassan II, B.P 7955,Sidi Othman, Casablanca, Morocco broumisaid78@gmail.com

Mohamed Talea Laboratory of Information Processing, Faculty of Science Ben M'Sik, University Hassan II, B.P 7955,Sidi Othman, Casablanca, Morocco taleamohamed@yahoo.fr Assia Bakali Ecole Royale Navale ,Boulevard Sour Jdid,B.P 16303 Casablanca, Morocco assiabakali@yahoo.fr

Florentin Smarandache

Department of Mathematics, University of New

Mexico, 705 Gurley Avenue, Gallup, NM,

87301, USA

fsmarandache@gmail.com; smarand@unm.edu

Mohsin Khan

Department of Mathematics, Abdul Wali Khan University,

Mardan 23200, Pakistan

mohsinkhan7284@gmail.com

#### **ABSTRACT**

In this research paper, the graph of the bipolar single-valued neutrosophic set model (BSVNS) is proposed. The graphs of single valued neutrosophic set models is generalized by this graph. For the BSVNS model, several results have been proved on complete and isolated graphs. Adding, an important and suitable condition for the graphs of the BSVNS model to become an isolated graph of the BSVNS model has been demonstrated.

## **KEYWORDS**

Bipolar single valued neutrosophic graphs (BSVNG), complete-BSVNG, isolated-BSVNGs.

## 1 Introduction

The concept of 'Neutrosophic logic' was developed by Prof. Dr. F. Smarandache in 1995 and get published in 1998. "It is a branch of philosophy which studies the origin, nature, and scope of neutralities, as well as their interactions with different ideational spectra" [4]. The concepts of fuzzy sets [8] and intuitionistic fuzzy set [6] were generalized by adding an independent indeterminacy-membership. Neutrosophic logic is a powerful tool to deal

with incomplete, indeterminate, and inconsistent information, which is the main reason for widespread concerns of researchers. The concept of neutrosophic set(NS for short) is characterized by three independent degrees namely truthmembership indeterminacydegree (T), membership degree (I), and falsity-membership degree (F). To practice NSs in real life situations efficiently, The subclass of the neutrosophic sets called single-valued neutrosophic set (in short SVNS) was defined by Smarandache in [4]. In another paper [5], Wang et al. defined the various operations and operators for the SVNS model. In [11] Deli et al. proposed a new concept called bipolar neutrosophic sets. This concept appear as a generalization of fuzzy sets, intuitionistic fuzzy sets, bipolar fuzzy sets, bipolar intuitionistic fuzzy sets and single valued neutrosophic set. The benefits of applying the NSs have been addressed in [18]. The theory of graphs is the mostly used tool for resolving combinatorial problems in diverse disciplines like computer science, algebra and topology, etc. In [2, 4] Smarandache proposed two kinds of neutrosophic graphs to deal with situations in inconsistencies which there exist indeterminacies among the vertices which cannot be dealt with by fuzzy graphs and different hybrid structures including bipolar fuzzy graphs, intuitionistic fuzzy graphs, bipolar intuitionsite

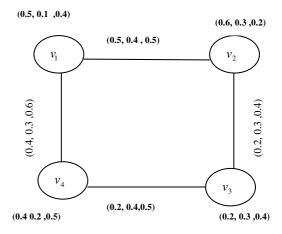

fuzzy graphs [1,7,9, 10], The first kind is based on literal indeterminacy (I) component, the second kind of neutrosophic graphs is based on numerical truth-values (T, I, F), Recently, a hybrid study by combining SVNS and classical graph theory was carried out and that concept is called Single valued neutrosophic graph (SVNG) was presented by Broumi et al [12, 13, 14, 17, 20, 22].In addition, the concept of bipolar neutrosophic set was combined with graph theory and new graph model was presented. This called bipolar single concept is valued neutrosophic graph (BSVNGs). In [15,16] Broumi et al. proposed the concept of bipolar valued neutrosophic graph generalized the concept of fuzzy graph, intuitionistic fuzzy graph, bipolar fuzzy graph and single valued neutrosophic graph.

The objective of this article is to demonstrate the essential and satisfactory condition of BSVNGs to be an isolated-BSVNG.

#### 2.Background of research

Some of the important background knowledge in this paper is presented in this section. These results can be found in [4, 5, 12,13,15, 21].